## ON-CHIP SOFTWARE TOOLS FOR HARDWARE MULTITASKING ON PARTIALLY RECONFIGURABLE FPGAS

Ву

AURELIO FEDERICO MORALES VILLANUEVA

A DISSERTATION PRESENTED TO THE GRADUATE SCHOOL

OF THE UNIVERSITY OF FLORIDA IN PARTIAL FULFILLMENT

OF THE REQUIREMENTS FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

UNIVERSITY OF FLORIDA

2015

#### **ACKNOWLEDGMENTS**

This work was supported by the Unidad Coordinadora del Programa de Ciencia y Tecnología (FINCyT), Perú, under contract N° 121-2009-FINCyT-BDE and in part by the I/UCRC Program of the National Science Foundation, under grants EEC-0642422 and IIP-1161022. The author gratefully acknowledges the support of Universidad Nacional de Ingeniería – Lima, Perú, the Presidencia del Consejo de Ministros in Perú, through FINCyT, and the tools provided by Xilinx.

Special thanks to Dr. Alan George, director of the NSF Center for High-Performance Reconfigurable Computing (CHREC), who gave me the chance to be part of this prestigious center as a research volunteer. And finally, I would like to thank my Ph.D. advisor, Dr. Ann Gordon-Ross, for all of her guidance and support throughout the last several years.

# TABLE OF CONTENTS

|     |      | <u>p</u>                                                          | <u>age</u> |

|-----|------|-------------------------------------------------------------------|------------|

| AC  | KNOV | VLEDGMENTS                                                        | 4          |

| LIS | T OF | TABLES                                                            | 7          |

| LIS | T OF | FIGURES                                                           | 9          |

| AB  | STRA | CT                                                                | . 11       |

| СН  | APTE | R                                                                 |            |

| 1   | INTR | ODUCTION                                                          | . 13       |

| 2   | BAC  | KGROUND AND RELATED RESEARCH                                      | . 19       |

|     | 2.1  | Previous Work                                                     | . 19       |

|     | 2.2  | Virtex-5 FPGA architecture                                        |            |

|     |      | 2.2.1 Device Layout and Resources                                 |            |

|     |      | 2.2.2 Device Configuration                                        |            |

|     |      | 2.2.3 Cost Model for Partial Bitstream Size                       | . 29       |

| 3   |      | CHIP CONTEXT SAVE AND RESTORE, AND HARDWARE TASK OCATION SOFTWARE | 33         |

|     | IXEL | SOATION SOI TWANE                                                 | . 55       |

|     | 3.1  | CSR and HTR Overview                                              | . 34       |

|     | 3.2  | Context Save (CS) of Hardware Tasks                               | . 35       |

|     | 3.3  | Merge of Initial Bitstream and Saved Context                      |            |

|     | 3.4  | Saved Context Relocation of Hardware Tasks (HTR)                  | . 38       |

|     | 3.5  | Context Restore (CR) of Hardware Tasks                            |            |

|     | 3.6  | CSR and HTR Portability across FPGA Device Families               | . 41       |

|     | 3.7  | Summary                                                           | . 45       |

| 4   | ON-C | CHIP DISTRIBUTED DYNAMIC RESOURCE MANAGEMENT SOFTWARE             | . 49       |

|     | 4.1  | DDRM Concepts and Definitions                                     | . 50       |

|     | 4.2  | DDRM Overview                                                     |            |

|     | 4.3  | DDRM Operations                                                   |            |

|     | 4.4  | Summary                                                           |            |

| 5   | EXP  | ERIMENTAL RESULTS                                                 | . 75       |

|     | 5.1  | Experimental setup                                                |            |

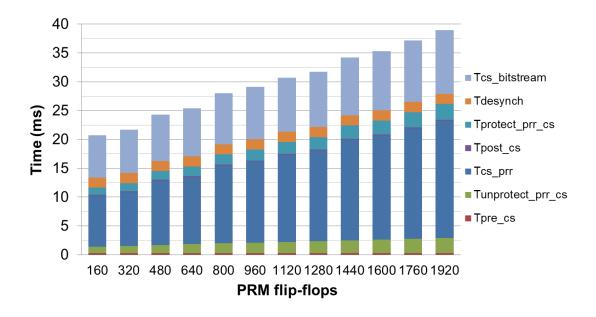

|     | 5.2  | CSR Experimental Results                                          |            |

|     | 5.3  | HTR Experimental Results                                          |            |

|     | 5.4  | DDRM Experimental Results                                         | . 88       |

| 6   | CONCLUSIONS       | 106 |

|-----|-------------------|-----|

| RE  | FERENCES          | 109 |

| BIC | OGRAPHICAL SKETCH | 114 |

# LIST OF TABLES

| <u>Table</u> | Ξ                                                                                                                                | <u>age</u> |

|--------------|----------------------------------------------------------------------------------------------------------------------------------|------------|

| 2-1          | Parameters used in the partial bitstream size cost model                                                                         | 31         |

| 2-2          | Specific values from Table 2-1 for Virtex-4/5/6 FPGA device families                                                             | 32         |

| 3-1          | Truth table for the CSR merge process                                                                                            | 46         |

| 4-1          | Global table for local and remote PRM relocation for node consistency in DDRM with two nodes                                     | 70         |

| 4-2          | Local table for node consistency in DDRM showing the currently assigned PRMs in node "1" from Table 4-1                          | 70         |

| 5-1          | CS bitstream and partial bitstream sizes (in KB) used in the CSR, HTR, and DDRM experiments                                      | 93         |

| 5-2          | Execution times (ms) for Treconfig_prr                                                                                           | 93         |

| 5-3          | Execution times (ms) for CS (Tcs) in CSR                                                                                         | 94         |

| 5-4          | Execution times (ms) for the merge process ( <i>T<sub>merge</sub></i> ) in CSR                                                   | 94         |

| 5-5          | Execution times (ms) for CR ( <i>T<sub>cr</sub></i> ) in CSR                                                                     | 94         |

| 5-6          | Execution times (ms) for CS ( $T_{cs}$ ), context relocation ( $T_{relocate}$ ), and CR ( $T_{cr}$ ) for small-to-large PRR HTR. | 95         |

| 5-7          | Execution times (ms) for CS ( $T_{cs}$ ), context relocation ( $T_{relocate}$ ), and CR ( $T_{cr}$ ) for large-to-small PRR HTR. | 95         |

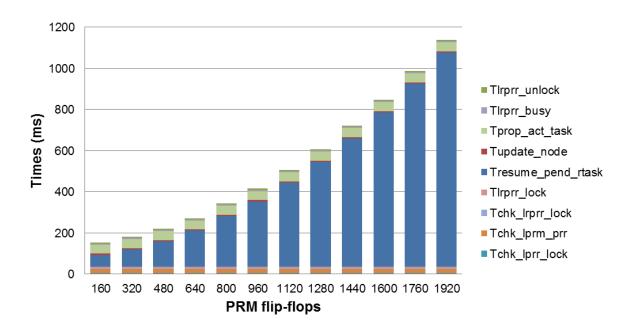

| 5-8          | DDRM execution times (ms) for $T_{\text{exe1}}$ with respect to the number of PRM flip-flops.                                    | 95         |

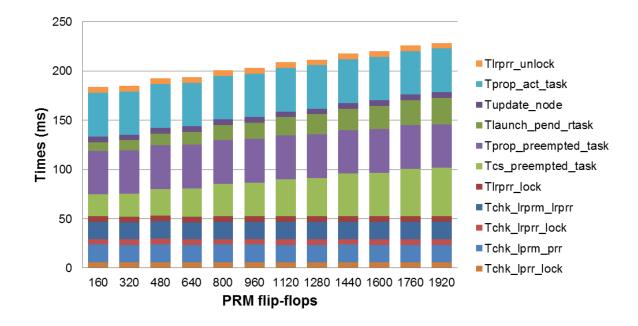

| 5-9          | DDRM execution times (ms) for $T_{res1}$ with respect to the number of PRM flip-flops.                                           |            |

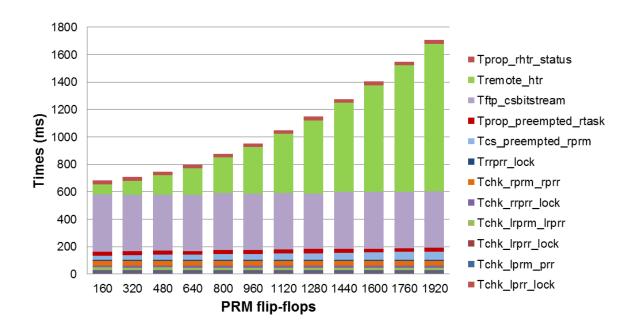

| 5-10         | DDRM execution times (ms) for $T_{\text{exe2}}$ with respect to the number of PRM flip-flops (part 1 of 2)                       | 96         |

| 5-11         | DDRM execution times (ms) for $T_{\text{exe2}}$ with respect to the number of PRM flip-flops (part 2 of 2)                       | 96         |

| 5-12         | DDRM execution times (ms) for $T_{res3}$ with respect to the number of PRM flip-flops (part 1 of 2)                              | 97         |

| 5-13 | DDRM execution times (ms) for $T_{res3}$ with respect to the number of PRM flip-flops (part 2 of 2)           | . 97 |

|------|---------------------------------------------------------------------------------------------------------------|------|

| 5-14 | DDRM execution times (ms) for $T_{\text{exe4}}$ with respect to the number of PRM flip-flops (part 1 of 2)    | . 97 |

| 5-15 | DDRM execution times (ms) for $T_{\text{exe4}}$ with respect to the number of PRM flip-flops (part 2 of 2)    | . 98 |

| 5-16 | DDRM execution times (ms) for $T_{\text{exeres2}}$ with respect to the number of PRM flip-flops (part 1 of 2) | . 98 |

| 5-17 | DDRM execution times (ms) for $T_{\text{exeres2}}$ with respect to the number of PRM flip-flops (part 2 of 2) | . 98 |

# LIST OF FIGURES

| Figure | <u>e</u>                                                                                                                                                                                                                                                                                          | <u>age</u> |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 2-1    | Virtex-5 LX110T FPGA fabric layout with four sample PRRs                                                                                                                                                                                                                                          | 32         |

| 2-2    | Partial bitstream structure for Virtex-5 FPGAs                                                                                                                                                                                                                                                    | 32         |

| 3-1    | On-chip context save and restore (CSR) and hardware task relocation (HTR) flows                                                                                                                                                                                                                   | 47         |

| 3-2    | Multiple flip-flop updates for CSR merge process                                                                                                                                                                                                                                                  | 47         |

| 3-3    | Single flip-flop update for context relocation (HTR) process                                                                                                                                                                                                                                      | 47         |

| 3-4    | Multiple flip-flop updates in a word boundary for context relocation (HTR) process                                                                                                                                                                                                                | 48         |

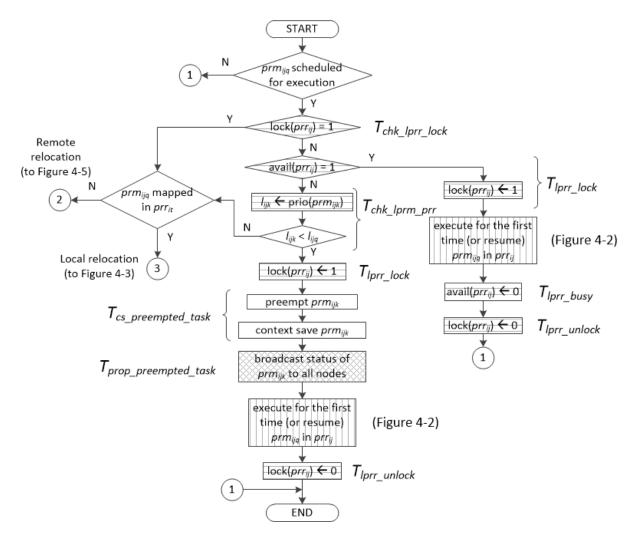

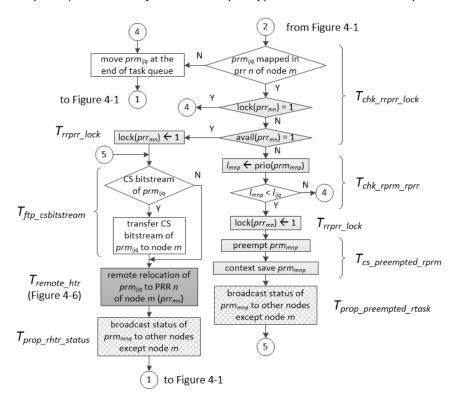

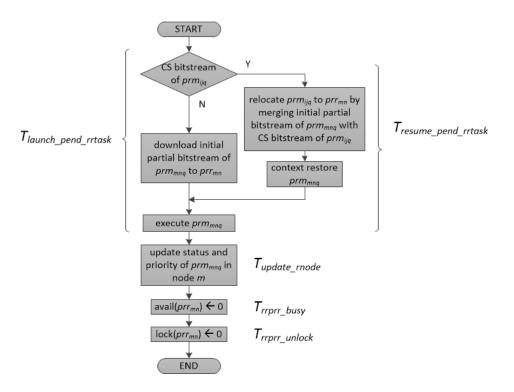

| 4-1    | Portion of the distributed dynamic resource management (DDRM) flow showing the first time execution (or resumption) of a PRM <i>prm<sub>ijq</sub></i> in a predefined PRR <i>prr<sub>ij</sub></i>                                                                                                 | 71         |

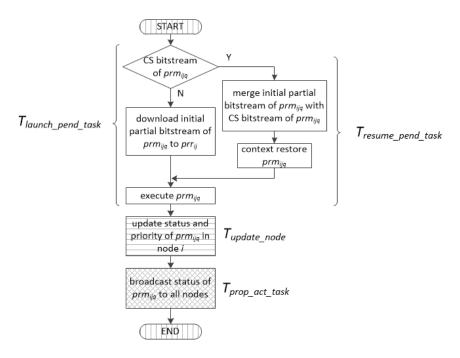

| 4-2    | Details of the DDRM flow for the steps performed in the boxes with vertical lines in Figure 4-1 for the first time execution (or resumption) of $prm_{ijq}$ in predefined $prr_{ij}$ .                                                                                                            | 72         |

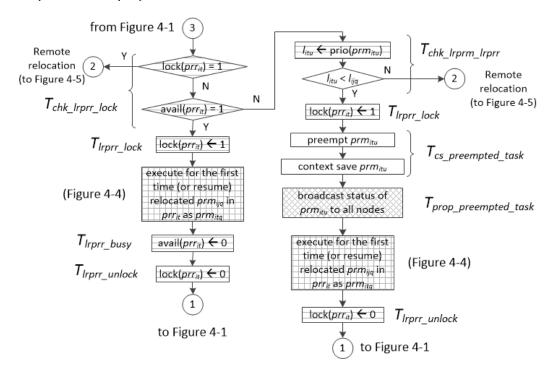

| 4-3    | DDRM flow continued, showing the first time execution (or resumption) of a locally relocated <i>prm<sub>ijq</sub></i> in a local candidate <i>prr<sub>it</sub></i> as <i>prm<sub>itq</sub></i>                                                                                                    | 72         |

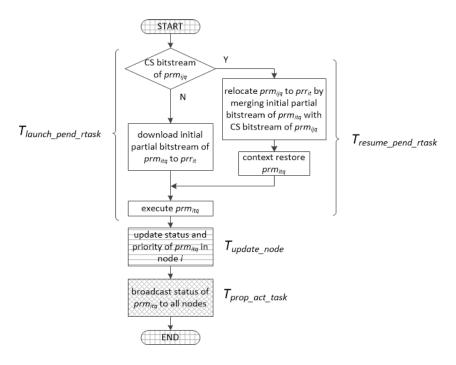

| 4-4    | Detailed steps of the DDRM flow showing the steps performed in the boxes with horizontal and vertical lines from Figure 4-3 for the first time execution (or resumption) of a locally relocated <i>prm<sub>ijq</sub></i> in a local candidate <i>prr<sub>it</sub></i> as <i>prm<sub>itq</sub></i> | 73         |

| 4-5    | DDRM flow continued, showing the execution of the remote relocation of $prm_{ijq}$ to a remote candidate PRR $n$ in a node $m$ ( $prr_{mn}$ ) as $prm_{mnq}$                                                                                                                                      | 73         |

| 4-6    | DRRM flow continued, showing the steps performed in the dark gray box in Figure 4-5 for execution of the remote relocation of $prm_{ijq}$ to a remote candidate PRR $n$ in node $m$ ( $prr_{mn}$ ) as $prm_{mnq}$ .                                                                               | 74         |

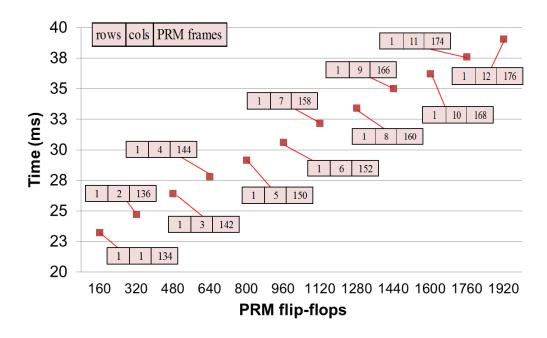

| 5-1    | Execution times (ms) for $T_{reconfig\_prr}$ with respect to the number of PRM flip-flops                                                                                                                                                                                                         | 99         |

| 5-2    | Execution times (ms) for CS ( $T_{cs}$ ) in CSR with respect to the number of PRM flip-flops                                                                                                                                                                                                      | 99         |

| 5-3    | Execution times (ms) for the merge process ( $T_{merge}$ ) in CSR with respect to the number of PRM flip-flops                                                                                                                                                                                    | 00         |

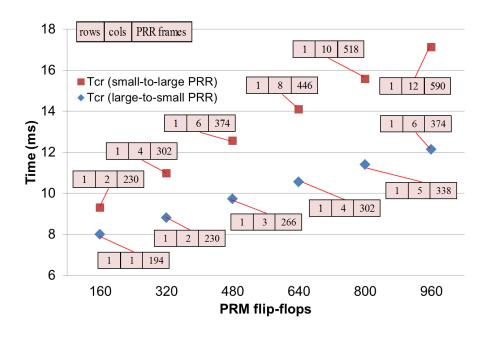

| 5-4  | Execution times (ms) for CR ( $T_{cr}$ ) in CSR with respect to the number of PRM flip-flops                       | 100 |

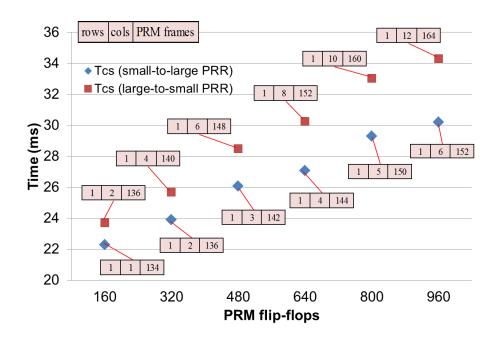

|------|--------------------------------------------------------------------------------------------------------------------|-----|

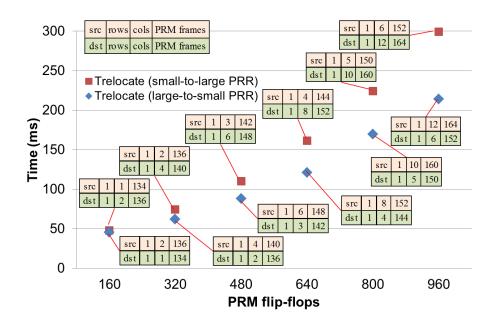

| 5-5  | Execution times (ms) for CS ( $T_{cs}$ ) in HTR with respect to the number of PRM flip-flops                       | 101 |

| 5-6  | Execution times (ms) for context relocation ( $T_{relocate}$ ) in HTR with respect to the number of PRM flip-flops | 101 |

| 5-7  | Execution times (ms) for CR ( $T_{cr}$ ) in HTR with respect to the number of PRM flip-flops                       | 102 |

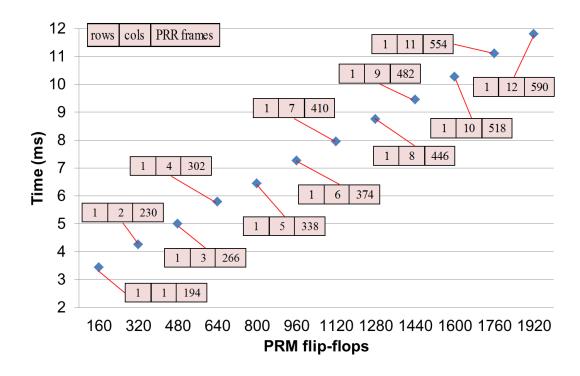

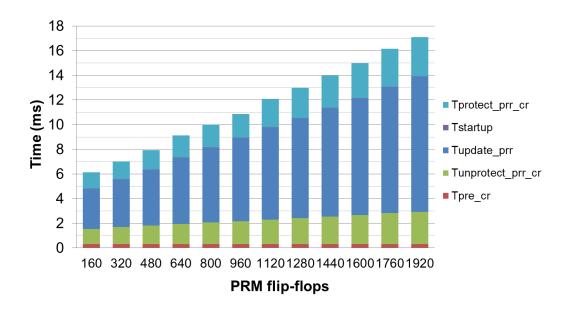

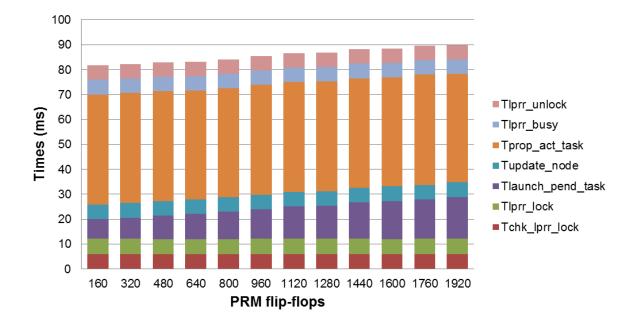

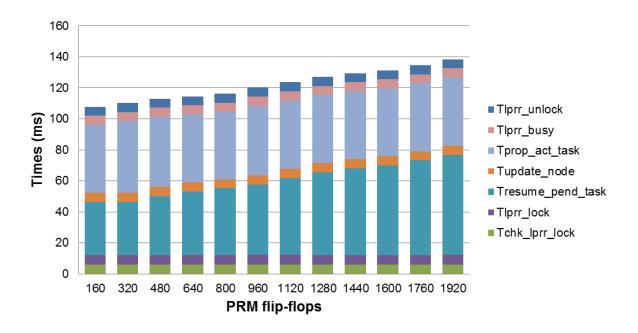

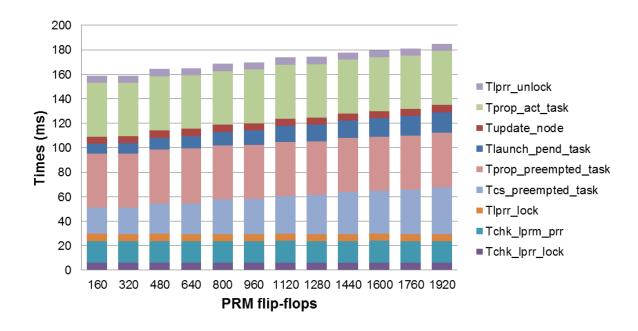

| 5-8  | DDRM execution times (ms) for $T_{\text{exe1}}$ with respect to the number of PRM flip-flops                       | 102 |

| 5-9  | DDRM execution times (ms) for $T_{res1}$ with respect to the number of PRM flip-flops                              | 103 |

| 5-10 | DDRM execution times (ms) for $T_{\text{exe2}}$ with respect to the number of PRM flip-flops                       | 103 |

| 5-11 | DDRM execution times (ms) for $T_{res3}$ with respect to the number of PRM flip-flops                              | 104 |

| 5-12 | DDRM execution times (ms) for $T_{\text{exe4}}$ with respect to the number of PRM flip-flops                       | 104 |

| 5-13 | DDRM execution times (ms) for $T_{\text{exeres2}}$ with respect to the number of PRM flip-flops                    | 105 |

Abstract of Dissertation Presented to the Graduate School of the University of Florida in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

# ON-CHIP SOFTWARE TOOLS FOR HARDWARE MULTITASKING ON PARTIALLY RECONFIGURABLE FPGAS

By

#### Aurelio Federico Morales Villanueva

August 2015

Chair: Ann Gordon-Ross

Major: Electrical and Computer Engineering

Partially reconfigurable (PR) field-programmable gate arrays (FPGAs) partition the FPGA into one static region and multiple PR regions (PRRs). This partitioning affords faster reconfiguration time, as compared to configuring the entire FPGA since the PRRs are reconfigured using smaller partial bitstreams. PR FPGAs also afford isolated reconfiguration since only the reconfigured PRR halts execution while the remainder of the FPGA continues to operate. Faster and isolated reconfiguration enable flexible hardware task multiplexing in the PRRs, and, to fully exploit this PRR time multiplexing, higher priority tasks should be able to preempt lower priority tasks, and the preempted tasks should be able to resume execution in any PRR with sufficient resources. This preemption/resumption requires saving/restoring the preempted task execution context and relocating the task to another PRR.

Some prior works address the involved challenges, but these works only provide partial solutions and impose limitations and/or overheads that prevent portability of these works across different FPGA device families. The research presented here presents a set of methods and software tools for hardware multitasking on PR FPGAs to address prior works' limitations.

11

First, we present on-chip context save and restore (CSR) software to enable task preemption/resumption in the same PRR, preserving the execution state of preempted hardware tasks, without disrupting operations in the static region and other PRRs in the FPGA. Second, we introduce on-chip hardware task relocation (HTR) software to enable a task execution state to be saved, and relocated to and restored in any PRR in the FPGA with sufficient resources. Finally, using our on-chip HTR software, we present on-chip distributed dynamic resource management (DDRM) for PR FPGAs to enable context relocation of hardware tasks between different physical FPGAs on an interconnected network. Experimental results evaluate CSR, HTR, and DDRM execution times, enabling designers to tradeoff task/PRR granularity and CSR/HTR/DDRM execution times based on application requirements.

# CHAPTER 1 INTRODUCTION

Partially reconfigurable (PR) field programmable gate arrays (FPGAs) partition the FPGA fabric into one static region and one or more PR regions (PRRs). This partitioning enables PRRs to time multiplex hardware tasks, where incoming tasks can be scheduled to any *candidate* PRR, which is any free/idle PRR (not currently executing another task) with sufficient resources. This resource time multiplexing reduces the total FPGA area requirements and power consumption, since smaller FPGA devices can be used. Also, this partitioning can improve overall PR system performance compared to not using PRRs or using non-PR FPGAs.

PRRs are reconfigured using small partial bitstreams, which affords faster reconfiguration times as compared to using full bitstreams that are used to configure the entire FPGA. Reconfiguring a PRR is isolated, where only the scheduled PRR halts operation during the reconfiguration, while the static region and the other PRRs continue executing. This isolated PRR reconfiguration enables maximum flexibility and adherence to task priority requirements using task preemption and resumption, where higher priority tasks can preempt lower priority tasks on scheduled PRRs.

Task preemption/resumption pauses/resumes task execution by saving/restoring the task's execution state (i.e., context). Resumed tasks can be scheduled to any candidate PRR, wherein a candidate PRR now includes any PRR with sufficient resources that is currently executing a lower priority task, which will be preempted. Task preemption requires a context save (CS) operation, which reads the task's execution state from the FPGA and saves this context off-chip in a CS bitstream.

Task resumption requires a context restore (CR) operation using the previously saved CS bitstream to restore the task's execution state on the scheduled PRR. To effectively restore the task's execution state, the CS bitstream is merged with the task's initial partial bitstream (created at synthesis), where the merged bitstream is created using bitstream manipulations using bit-level and 32-bit word-level bit masking.

There exist some prior works on CS and CR—collectively referred to as context save and restore (CSR)—to the same PRR [14][22][23][24][26][35]. However, requiring that CR only be to the same PRR is too restrictive, and hardware tasks should be able to resume execution in any candidate PRR. Hardware task relocation (HTR) alleviates this restriction by relocating and resuming task execution in any candidate PRR, which affords improved performance/task throughput, and maximizes resource usage, especially for application domains such as dynamic load balancing of hardware tasks and task migration across different network-connected FPGAs (e.g., local wired network, wireless network, etc.).

HTR is more challenging than CSR because the relocation and resumption of a preempted task is a complex process. HTR is relatively easy when relocating tasks between homogenous PRRs (same size, shape, and resource distribution, but different fabric location), since the bitstream manipulation is relatively simple [26][29]. However, relocating tasks between only homogeneous PRRs impose many restrictions [2][3][11] that prevent portability across different FPGA device families. HTR for task relocation between different-sized heterogeneous PRRs (different shape, resource distribution, and fabric location) is significantly more challenging.

Prior works addressed some of the HTR challenges, such as bitstream relocation (BR) between homogeneous PRRs [4][7][8][9][10][16][30][36][39][41][42] or between same-sized heterogeneous PRRs [1][2]. However, BR does not save/restore the task's current execution state, and as a consequence, the task must be restarted when the task is relocated and resumed in another PRR, which introduces performance-degrading re-execution overhead that may involve seconds/minutes to re-generate data. We note that these prior works on HTR/BR do not address task relocation between different-sized heterogeneous PRRs.

Prior works on HTR evaluated off-chip and on-chip implementations. In off-chip HTR between homogeneous PRRs [26][29], the FPGA is attached to a host CPU that executes software-based HTR, imposing a dedicated communication bus between the host CPU and the FPGA, which introduces reconfiguration time overhead due to this communication. Additionally, this host CPU-FPGA dedicated communication bus prevents autonomous HTR implementation (i.e., the FPGA *must* have an attached CPU, and cannot execute autonomously in remote environments).

To enable autonomous HTR and eliminate this CPU-FPGA communication overhead, on-chip HTR can be implemented entirely on the FPGA either using custom hardware [3][17][18] or software running on a soft-core processor in the static region, or a combination of these two solutions [19][20]. Custom hardware on the FPGA generates area overhead, imposes device-specific constraints that limits portability across different FPGA device families, and reduces the task's maximum operating frequency.

Alternatively, on-chip software-based HTR enables system portability across different FPGA device families, does not generate area overhead, does not impose device-

specific constraints, and does not reduce the task's maximum operating frequency. We note that, to the best of our knowledge, there is no prior work on autonomous HTR that is portable across different FPGA device families that supports CR of hardware tasks between different-sized heterogeneous PRRs.

This research addresses prior CSR/BR/HTR works' limitations (e.g., area overhead due to using custom and non-portable on-chip hardware, host CPU-FPGA communication overhead, relocated task re-execution, etc.).

In the first phase of this research, we introduce on-chip CSR software for any heterogeneous PRR, where we leverage PR FPGAs' features for hardware multitasking on the same PRR, preserving the execution state of preempted hardware tasks, without disrupting operations in the static region and other PRRs, and where the on-chip CSR software executes on a soft-core processor in the FPGA's static region.

In the second phase of this research, we extend our on-chip CSR software to enable hardware multitasking between different PRRs in the same FPGA, and present on-chip HTR software for relocating hardware tasks' contexts between different-sized heterogeneous PRRs in order to maximize shared resources (PRRs) utilization, and maximize tasks throughputs.

In the third phase of this research, we further extend our HTR to function across multiple networked-interconnected FPGAs to enable dynamic CR of hardware tasks between physically-distributed devices. This extension provides additional improvements in task throughput due to more candidate PRRs, improvements in resource usage per FPGA, and vastly increases the application-domain applicability. To the best of our knowledge, no prior work proposes such a flexible HTR implementation.

We leverage our HTR for multiple interconnected FPGAs and present distributed dynamic resource management (DDRM), where each FPGA in the network is an autonomous system. DDRM can be used for application domains, such as dynamic load balancing of hardware tasks between FPGAs, distributed fault tolerant systems, and distributed, concurrent, and parallel processing of hardware tasks in a network of FPGAs.

We present a detailed description of the on-chip CSR/HTR/DDRM operations and present implementation results for a Virtex-5 LX110T with a MicroBlaze soft-core processor (used as the reconfiguration controller) running embedded Linux. Even though we show results for a specific FPGA device, since our CSR/HTR/DDRM uses the FPGA's internal configuration access port (ICAP), our CSR/HTR/DDRM software is portable (with minimum changes) to newer Xilinx device families, such as the Virtex-6, 7 series, and Zynq-7000.

Our on-chip CSR/HTR/DDRM executes on autonomous FPGA systems, which does not incur host CPU-FPGA communication overhead, does not introduce device overhead, does not impact the tasks' maximum operating frequencies, and is portable across different FPGA device families with minimum changes. Also, our CSR/HTR/DDRM maximizes PRR usage per FPGA, enabling the execution, preemption, and resumption of hardware tasks between different-sized heterogeneous PRRs without losing the preempted task's execution state, which eliminates seconds/minutes of re-execution time and reduces the task's waiting time by relocating the task to any candidate PRR on the same or a different FPGA. Additionally, our

analyses enable system designers to trade off CSR/HTR/DDRM execution times and task granularity (i.e., the task's PRR size) based on application requirements.

The organization of the remainder of this document is as follows. Background of the Virtex-5 FPGA architecture and device configuration, and related research pertaining to CSR, BR, and HTR is summarized in Chapter 2. Chapter 3 describes our on-chip CSR and HTR software, covering the major steps involved in CSR and HTR, and the portability of CSR/HTR across FPGA device families. Next, Chapter 4 discusses the details of how to extend our on-chip HTR software for multiple networked-interconnected FPGAs and presents the on-chip DDRM software. Chapter 5 then presents the experimental results of our on-chip CSR, HTR and DDRM software. Finally, Chapter 6 presents the conclusions of this research and outlines directions for possible future research.

# CHAPTER 2 BACKGROUND AND RELATED RESEARCH

The background and related research in this chapter is divided into two sections. Section 2.1 discusses prior works in the areas of CSR, BR and HTR, and Section 2.2 provides a background of Virtex-5 FPGA architecture, covering the device layout and resources, device configuration, and a cost model for partial bitstream size, which enable system designers to understand the fundamentals of our proposed on-chip software-based tools for hardware multitasking on PR FPGAs.

#### 2.1 Previous Work

There exists some prior works in CSR and of these works, few leverage PR FPGAs. Landaker et al. [31] and Simmler et al. [40] presented off-chip CSR methods where all CSR operations executed in software running on an attached host CPU. Since these works did not leverage PR FPGAs, CSR reconfigured the entire FPGA.

Landaker's work reported 407 ms, 465 ms, and 365 ms for CS, bitstream manipulations, and CR execution times, respectively, for a Xilinx Virtex XCV1000 device, while Simmler's work reported 14.4 ms, 83.7 ms, and 12.4 ms for the same execution times on a Xilinx Virtex XCV400 device.

Joswik et al. [24] presented off-chip CSR methods for PRRs, as opposed to the entire FPGA, and reduced CSR times using direct memory access (DMA) for the ICAP. The results showed CS and CR execution times on the order of hundreds of microseconds, and bitstream manipulation execution times on the order of a few milliseconds for a Xilinx Virtex-4 XC4VFX60 device. Additionally, Kalte and Porrmann [26] and Koester et al. [29] extended off-chip CSR between homogeneous PRRs by incorporating an on-chip custom hardware relocator (REPLICA and REPLICA2Pro, for

Kalte's and Koester's works, respectively). Results showed CS execution times ranging from 33 µs to 1.2 ms, CR execution times ranging from 190 µs to 7.0 ms, and relocation times ranging from 0.4 ms to 15.0 ms. However, both works were implemented for older Xilinx PR-capable FPGAs (Virtex-E XCV2000E and Virtex-II XC2V4000 devices, for REPLICA and REPLICA2Pro, respectively) that only supported one-dimensional (1-D) PRRs, and thus are not applicable to newer Xilinx devices that support two-dimensional (2-D) PRRs.

To eliminate the communication overhead between the FPGA and the host CPU, Koch et al. [28], Garcia et al. [14], and Jovanovic et al. [22] presented on-chip CSR hardware solutions (for non-PR FPGAs in Koch's work, and for PR FPGAs in Garcia's and Jovanovic's works). All these works reduced CS and CR times to the order of microseconds using different versions of scan-path chains of flip-flops, a technique used in design for testability (DFT) for very large scale integrated (VLSI) circuits. Additionally, Jozwik et al. [23] presented a task-specific access structure (TSAS) method to perform CSR, which inserted custom logic for each flip-flop and the FPGA's internal memory elements for each task to perform CS and CR, achieving CS and CR execution times from hundreds of microseconds to a few milliseconds. However, even though these methods eliminated communication with a host CPU, these methods incurred significant hardware overhead, lacked portability, reduced the system's maximum operating frequency, and required changes in the design tool flow. In prior work [35], we presented on-chip software CSR, which alleviated these drawbacks, but did not relocate the task to a different PRR.

BR enables task relocation, but prior works did not relocate the task's context to a different PRR. Horta and Lockwood [16], Blodget et al. [4], and Krasteva et al. [30] presented off-chip BR software, and Kalte et al. [25][27] presented on-chip BR hardware support for off-chip BR software. All of these prior works were intended for BR between homogeneous PRRs, however, these methods still incurred the same drawbacks as off-and on-chip CSR. Horta's work presented PARBIT to enable BR on Xilinx Virtex-E devices, Blodget's work introduced XPART to enable BR on Xilinx Virtex-II and Virtex-II Pro devices, and Krasteva's work presented BITPOS to enable BR on Xilinx Virtex-II devices. Krasteva's and Horta's works reported BR execution times of approximately 500 ms, while Blodget's works did not report BR execution times. Kalte's works used REPLICA and REPLICA2Pro, establishing a custom on-chip communication bus to enable all hardware tasks to communicate to each other, and obtained BR execution times on the order of milliseconds.

Becker et al. [1][2] and Carver et al. [7] presented on-chip BR software for same-sized heterogeneous PRRs and homogeneous PRRs, respectively, however, these methods constrained the static region's logic routing from passing through the PRRs, in addition to other constraints. Whereas these constraints reduced the number of partial bitstreams to one per task, the constraints introduced area and performance overheads [7][13]. Becker's and Carver's works reported BR throughputs of up to 4.7 MB/s and 9.5 MB/s, respectively, for Xilinx Virtex-4 devices. The partial bitstreams where stored in external flash memory and in the FPGA's internal random access memory blocks (BRAMs) for Becker's and Carver's work, respectively. Both authors used the on-chip MicroBlaze soft-core processor to execute the BR software.

Corbetta et al. [8][9], Morandi et al. [36], Sudarsanam et al. [42], Dasu and Kallam [10], and Sreeramareddy et al. [41] presented custom on-chip BR hardware for homogeneous PRRs, which was orchestrated using an on-chip soft-core processor. Corbetta's and Morandi's works used 1-D BiRF (for Virtex-II Pro devices) and 2-D BiRF (for Virtex-4/5 devices), and achieved BR throughputs of 5.9 MB/s and 7.3 MB/s for 1-D and 2-D BiRF, respectively. Sudarsanam's, Dasu's, and Sreeramareddy's works used ARC for Virtex-4 devices, and used BRAMs to reduce the BR execution times. Sudarsanam's and Sreeramareddy's works achieved BR throughputs of up to 65.6 MB/s and 86.3 MB/s, respectively. All these prior works used the on-chip MicroBlaze soft-core processor to orchestrate the on-chip BR hardware implementations. Even though Santambrogio et al. [39] used the 2-D BiRF for Xilinx Virtex-4 devices, that work did not use an on-chip processor to perform BR, and resulted in an average BR throughput of 740 MB/s.

There are a few prior works that focus on on-chip HTR. Iturbe et al. [17] proposed a custom hardware communication interface (CIF) that was attached to each hardware task to enable on-chip HTR between arbitrary heterogeneous PRRs for Virtex-4 devices. Also, Iturbe et al. [18] proposed Snake, a novel technique for hardware task allocation to enable inter-task communication between hardware tasks. Iturbe et al. [19][20] leveraged their prior work with CIF and Snake to propose a reliable reconfigurable real-time operating system (R3TOS) using one MicroBlaze and three PicoBlaze on-chip soft-core processors, where inter-task communication between hardware tasks was implemented with custom hardware data relocation task (DRT) blocks. However, Iturbe's CIFs used BRAMs (which are limited in number, and location-

specific FPGA storage resources) as buffers to hold input and output values in hardware tasks, and PRRs needed to be placed close to each other and to the DRTs on the FPGA fabric, imposing area overhead and specific constraints, which prevented portability of Iturbe's on-chip HTR solution across FPGA device families.

In order to address the drawbacks of prior off- and on-chip CSR, BR, and HTR methods (e.g., high communication overhead and device resource overhead, lack of system portability, and reduced maximum operating frequency, respectively) and to improve system performance and flexibility via task preemption/resumption/relocation, we propose in this document on-chip CSR software for CS and CR on any arbitrary 2-D PRR, and on-chip HTR software for 2-D different-sized heterogeneous PRRs. The CSR and HTR software executes on a soft-core processor in the FPGA's static region and uses the ICAP for reconfiguration. As compared to similar prior works, our CSR and HTR do not incur off-chip communication overhead, do not introduce hardware/device overhead, do not impact the tasks' maximum operating frequency, has no special constraints on the PRRs and static region (e.g., as in [1][2][7][11][18][19]), and do not require tool flow changes.

#### 2.2 Virtex-5 FPGA architecture

Since both CSR and HTR are complex processes that require detailed device knowledge, in this section we review the Xilinx Virtex-5 FPGA architecture, which will assist designers in incorporating HTR into their systems. We refer the reader to [50] and [51] for complete information on Virtex-5 device configuration and architecture, respectively.

## 2.2.1 Device Layout and Resources

The Virtex-5 devices support 2-D PRRs, which allows PRRs to occupy a rectangular fabric area. Prior Virtex families (Virtex, Virtex-E, Virtex-II, and Virtex-II Pro) only supported 1-D PRRs, which required PRRs to span the fabric's entire height. 2-D PRRs offers finer reconfiguration granularity and therefore, increases design flexibility and resource utilization. Virtex-5's can be configured using external interfaces, such as JTAG (serial), SelectMAP (parallel), or the internal ICAP interface (parallel).

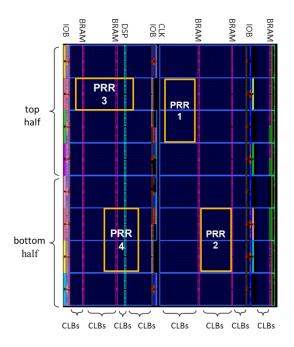

Figure 2-1 depicts the Virtex-5 LX110T device's fabric layout, the device used in our experiments, with four sample PRRs and the following resources [51]: configurable logic blocks (CLBs), which implement combinational and sequential logic and each CLB contains eight flip-flops; random access memory blocks (BRAMs) for internal storage; input/output blocks (IOBs), which are mainly used to provide external connections between the FPGA and other devices; digital signal processing blocks (DSPs) implement complex arithmetic functions that cannot be efficiently implemented using CLBs [52]; and clock resources (CLK) provide clock signals to all resources. Each CLB contains one slice pair. Each slice contains four logic-function generators (look-up tables or LUTs), four flip-flops, multiplexers, and carry logic. Slices denoted as SLICEMs support storing data using distributed RAM (or LUTRAM) and shifting data with 32-bit registers, and SLICELs do not support these functions. Across the entire device fabric, 50% of the CLB columns contain one SLICEM and one SLICEL, and the other 50% of the CLB columns contain two SLICELs.

As exemplified in Figure 2-1, the resources are distributed in the device fabric in a row/column organization. The device is logically divided into two halves—the top and bottom—and each half contains four rows and each row contains the same number of

columns. Each column contains a group of frames and the number of frames per column depends on the resource type (CLB, BRAM, etc.). A frame is the minimum unit of information used to write/read to/from the device. For Virtex-5 devices, a frame contains 41 32-bit words.

With respect to HTR, partial regions PRR1 and PRR2 are homogeneous since these PRRs have the same size (same number of columns and rows) and the same resources (CLBs), even though the PRRs' locations in the device fabric are different. Alternatively, partial regions PRR3 and PRR4 are heterogeneous since these PRRs have different sizes, resources, and device fabric locations. A special case of homogeneous PRRs would be if two PRRs have the same resources (CLBs, BRAMs, DSP, etc.), both PRRs begin at the same column and finish at the same column, have the same number of rows, but have different vertical positions. The minimum PRR size on the Virtex-5 is one row and one column.

#### 2.2.2 Device Configuration

A Xilinx PR FPGA can be configured using full or partial bitstreams, which are used to configure the entire device or only a single PRR, respectively. The bitstream's configuration information is organized in configuration frames and is stored in the FPGA's internal configuration memory. A configuration frame establishes the configuration of the resources of a specific column and the routing information to access the resources. For the Virtex-5 device family, CLB, BRAM, DSP, IOB, and CLK columns have 36, 30, 28, 54, and 4 configuration frames, respectively [50]. Additionally, each BRAM column requires 128 data frames for initialization.

Full configuration of the device requires sequential execution of three phases: the setup phase, the bitstream loading phase, and the startup sequence phase [50]. While

the configuration frames are downloading, the device continuously calculates the cyclic redundancy check (CRC) value. After downloading all of the configuration frames, the device verifies the CRC by comparing the calculated CRC with the bitstream's expected CRC, which is included as part of the bitstream. If the CRCs match, the startup sequence phase begins, which initializes the device's flip-flops and BRAMs, and the device enters the *user* mode by asserting the internal end of startup (EOS) signal and the external DONE pin.

Once the device is in user mode, partial reconfiguration of a PRR can be performed using the ICAP. PRR reconfiguration starts from the bitstream loading phase, and the startup sequence phase is not executed since the device is already in user mode, and the reconfigured PRR's flip-flops and BRAMs are reconfigured provided that CRC verification was successful. Since PRRs may contain flip-flops, BRAMs, and DSPs, dedicated clock gating (using buffer BUFGCE) is used for each PRR to enable changes in these resources for each clock transition. Since the FPGA has only one ICAP, it is not possible to perform more than one ICAP operation (read or write) at a time.

Future re-initialization of flip-flops and BRAMs can be forced by toggling the internal global set reset (GSR) signal using the Xilinx user primitive STARTUP\_VIRTEX5 in order to execute the startup sequence phase if the CRC verification is skipped [34]. However, since toggling the GSR would re-initialize the entire device with the flip-flops' and BRAMs' initial values as defined in the full bitstream, a protection/unprotection mechanism for the static region and PRRs must be

provided [34]. This mechanism avoids/allows future re-initialization of flip-flops and BRAMs when the GSR is toggled.

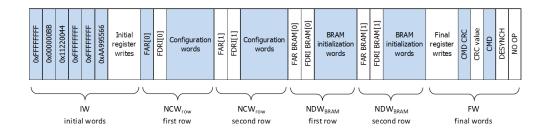

Since CSR/HTR leverages the ICAP, all partial bitstreams need to be 32-bit word aligned. Figure 2-2 depicts the initial partial bitstream structure used in CSR/HTR for the Virtex-5. This partial bitstream is the same as the bitstream that is generated by the Xilinx tools, with the exception that the initial comments, which include the name of the native circuit description file (\*.ncd) that was used to generate the bitstream and the bitstream's creation date, are extracted, resulting in a 32-bit word aligned file to be used with the ICAP. The initial partial bitstream consists of a sequence of initial words, including the bus width words (0x000000BB and 0x11220044), the synchronization word (0xAA995566), a sequence of initial register writes that includes the RCRC (reset CRC), IDCODE (0x02AD6093), WCFG, FAR (frame address register), and FDRI (frame data register input, which specifies the number of 32-bit configuration words to write into the device) [50], followed by the configuration words (number of which is specified by the FDRI), and ending with the final words, that includes the final register writes (MASK, CTL1, LFRM), the CRC, and DESYNCH (which releases the ICAP and allows other PRRs to be reconfigured) [50].

If the PRR consists of only one row with no BRAM columns, there is only one pair of FAR/FDRI values, which is followed by the configuration words. For a PRR with multiple rows with no BRAM columns, the partial bitstream uses as many pairs of FAR/FDRI values as number of rows in the PRR, which are followed by the configuration words for each row. If the PRR includes BRAM columns, additional pairs of FAR/FDRI are used for the BRAM initialization words, which follow the last row's

configuration words for the rows that contain BRAM columns. Figure 2-2 depicts a sample partial bitstream structure for a PRR with two rows that contain CLBs, DSPs, and BRAMs.

In order to read a task's context (i.e., CS), the command GCAPTURE [50] is sent to the device via the ICAP to capture the flip-flops' values on a single edge transition of the main clock. Reading the flip-flops' values from the device is defined by Xilinx as the readback capture process, denoted as capture for CSR/HTR purposes, which is different from the readback verify process (defined by Xilinx), where the flip-flops' initial values are read. After capturing the PRR's flip-flops' values, the command RCAP (reset capture) is sent via the ICAP to enable future CSs on the same or different PRR. We note that a protected PRR does not allow the task to capture the task's flip-flops and BRAMs values.

Restoring a task's context (i.e., CR) to a PRR requires initializing the PRR's flip-flops' values with the saved flip-flops' values (i.e., the task's context) without interrupting the static region or the other PRRs' executions. In order to initialize a PRR with new flip-flop values, the GSR signal must be toggled, however, since toggling this signal would re-initialize the entire device with the initial values defined in the full bitstream, a protection/unprotection mechanism must be provided.

A PRR/FPGA can be protected using the block type '010' and a special frame, sent to all PRR/FPGA columns, that has all 41 32-bit words set to 0x00000000 except word 21, which has bit 12 and 13 set to '1', which correspond to the internal GWE (global write enable) and GRESTORE signals, respectively. Unprotecting a PRR/FPGA is similar, except that all 41 32-bit words are set to 0x00000000. Protecting the entire

FPGA only needs to be done once, while unprotection/protection of the PRRs is required for each CS and CR.

For newer devices (e.g., the Virtex-6 and -7 series, and the Zynq-7000) and tools (e.g., starting from the Xilinx PlanAhead 14.3 tool [53]) the RESET\_AFTER\_RECONFIG = TRUE (RaR) constraint may be applied to PRRs in order to avoid the manual unprotection/protection of PRRs and manual protection of the static region after full configuration. The partial bitstream generated with this constraint contains the ICAP command sequence to protect the entire FPGA, unprotect/protect the PRR, and the GRESTORE and START commands [50] to force the startup sequence. However, for the purposes of CSR/HTR, the user requires generation of the CRC with custom hardware, which incurs hardware overhead (1,218 FFs and 5 BRAMs for the Virtex-4) [24], unless the CRC verification is skipped. Since partial bitstreams using the RaR constraint contain the ICAP commands to protect the entire FPGA, these partial bitstreams are extremely large in size as compared to partial bitstreams without using the RaR constraint, which increases the PRR reconfiguration time.

Additionally, for the purposes of physical implementation of CSR/HTR, the user would not have manual control of re-initialization of the PRR's flip-flops and BRAMs after downloading the partial bitstream if the RaR constraint is used, causing the task that is executing in that PRR to terminate. Thus, all of the fundamentals explained in this work for the Virtex-5 are still valid for the newer devices.

#### 2.2.3 Cost Model for Partial Bitstream Size

From the initial partial bitstream structure depicted in Figure 2-2, the partial bitstream size can be calculated using a simple cost model, which is used for the CSR, HTR, and DDRM experiments. Table 2-1 depicts the parameters for partial bitstream

size derivation where *IW*, *FW*, *FAR\_FDRI*, *CF<sub>CLB</sub>*, *CF<sub>DSP</sub>*, *CF<sub>BRAM</sub>*, *DF<sub>BRAM</sub>*, and *FR*<sub>size</sub> are device family dependent. We note that for Virtex-4/5/6 and Series 7 devices, words are 32-bit, however, in other devices, such as Spartan-3/6 devices, words are 16-bit, therefore, *Bytes<sub>word</sub>* must be adjusted according to the device family. In Table 2-1, the *FAR\_FDRI* specifies the number of words for setting the FAR and the FDRI registers [50]. The FAR specifies the first frame address in terms of a row and column on the device fabric for configuration words (or initialization words for BRAM columns, if BRAMs are used) in a given PRR row, and the FDRI specifies the number of configuration words (or initialization words for BRAM columns) for the given PRR row. Table 2-2 summarizes the specific values from Table 2-1 for Virtex-4/5/6 device families.

The size of the partial bitstream ( $S_{bitstream}$ ) for a PRR with H rows that contains CLBs, DSPs, and BRAMs is:

$$S_{bitstream} = \{IW + H \times (NCW_{row} + NDW_{BRAM}) + FW\} \times Bytes_{word}$$

(2-1)

where IW and FW in (2-1) denote the number of initial and final words in the partial bitstream, respectively. The number of configuration words in a PRR row (denoted as  $NCW_{row}$ ) in (2-1) is expressed as:

$$NCW_{row} = FAR\_FDRI + (NCF_{CLB} + NCF_{DSP} + NCF_{BRAM} + 1) \times FR_{size}$$

(2-2)

where  $FR_{size}$  in (2-2) denotes the frame size in words. The total number of configuration frames per CLB, DSP, and BRAM columns in a single row of a PRR (denoted as  $NCF_{CLB}$ ,  $NCF_{DSP}$ , and  $NCF_{BRAM}$ , respectively) are:

$$NCF_{CLB} = W_{CLB} \times CF_{CLB}$$

(2-3)

$$NCF_{DSP} = W_{DSP} \times CF_{DSP}$$

(2-4)

$$NCF_{BRAM} = W_{BRAM} \times CF_{BRAM}$$

(2-5)

where  $W_{CLB}$ ,  $W_{DSP}$ , and  $W_{BRAM}$  included in (2-3), (2-4), and (2-5) are the number of CLB, DSP, and BRAM columns in the PRR, respectively. Also,  $CF_{CLB}$ ,  $CF_{DSP}$ , and  $CF_{BRAM}$  in (2-3), (2-4), and (2-5) are the number of configuration frames per single CLB, DSP, and BRAM column, respectively.

Finally, the number of BRAM initialization words in a PRR row (denoted as  $NDW_{BRAM}$ ) in (2-1) is:

$$NDW_{BRAM} = FAR\_FDRI + (W_{BRAM} \times DF_{BRAM} + 1) \times FR_{size}$$

(2-6)

where  $DF_{BRAM}$  included in (2-6) are the number of data initialization frames per single BRAM column.

Table 2-1. Parameters used in the partial bitstream size cost model

| Parameter             | Description                                          |

|-----------------------|------------------------------------------------------|

| IW                    | Number of initial words in the partial bitstream     |

| FW                    | Number of final words in the partial bitstream       |

| FAR_FDRI              | FAR/FDRI initialization words per row                |

| $NCW_{row}$           | Number of configuration words in a PRR row           |

| $NDW_{BRAM}$          | Number of BRAM initialization words in a PRR row     |

| $NCF_{CLB}$           | Number of CLB configuration frames in a PRR row      |

| $NCF_{DSP}$           | Number of DSP configuration frames in a PRR row      |

| $NCF_{BRAM}$          | Number of BRAM configuration frames in a PRR row     |

| $CF_{CLB}$            | Number of configuration frames per CLB column        |

| $CF_{DSP}$            | Number of configuration frames per DSP column        |

| $CF_{BRAM}$           | Number of configuration frames per BRAM column       |

| $DF_{BRAM}$           | Number of data initialization frames per BRAM column |

| FR <sub>size</sub>    | Frame size in words                                  |

| Bytes <sub>word</sub> | Number of bytes per word                             |

| Н                     | Number of rows in the PRR                            |

| Sbitstream            | Size of partial bitstream in bytes                   |

Table 2-2. Specific values from Table 2-1 for Virtex-4/5/6 FPGA device families

| Parameter               | Virtex-4 | Virtex-5 | Virtex-6 |

|-------------------------|----------|----------|----------|

| <i>CF<sub>CLB</sub></i> | 22       | 36       | 36       |

| $CF_{DSP}$              | 21       | 28       | 28       |

| <b>CF</b> BRAM          | 20       | 30       | 28       |

| DF <sub>BRAM</sub>      | 64       | 128      | 128      |

| FR <sub>size</sub>      | 41       | 41       | 81       |

| IW                      | 12       | 16       | 20       |

| FW                      | 108      | 114      | 113      |

| FAR_FDRI                | 5        | 5        | 5        |

| <b>Bytes</b> word       | 4        | 4        | 4        |

Figure 2-1. Virtex-5 LX110T FPGA fabric layout with four sample PRRs

Figure 2-2. Partial bitstream structure for Virtex-5 FPGAs

# CHAPTER 3 ON-CHIP CONTEXT SAVE AND RESTORE, AND HARDWARE TASK RELOCATION SOFTWARE

In this chapter, we give a detailed description of the on-chip CSR and HTR software, which correspond to the first and second phases of this research, in order to enable hardware multitasking on the same and different PRRs, respectively, for PR FPGAs.

Our on-chip CSR/HTR for heterogeneous PRRs executes in software on a soft-core processor in the FPGA's static region. We assume that prior to CSR/HTR execution, the applications have already been synthesized and partitioned into multiple hardware tasks, the PRRs [47][48] and soft-core processor have been created, the system contains a scheduler that maps and schedules incoming tasks to PRRs, and all full and initial partial bitstreams and necessary files have been generated. We refer to a hardware task that is executing in a PRR as a partially reconfigurable module (PRM), and we note that since a PRM may be executed in more than one heterogeneous PRR at different times, all PRM's initial partial bitstreams for candidate PRRs must be generated prior to system execution. Even though a PRR may contain a mixture of resources (CLBs, BRAMs, DSPs, IOBs), in this chapter, we detail CSR/HTR for PRMs that use CLB, distributed RAM (LUTRAM) for CLBs, and BRAM resources only, however, our technique is equally applicable to heterogeneous PRRs that contain DSPs and/or IOBs that are not used by the PRM.

The remainder of this chapter is organized as follows. Section 3.1 presents an overview of CSR and HTR. Section 3.2 describes how to perform CS of hardware tasks to produce a CS bitstream, which is the first major step in CSR and HTR. Section 3.3 then describes the merge process, in order to generate a new partial bitstream based

on the CS bitstream, which is the second major step in CSR. Next, Section 3.4 describes how to perform the saved context relocation between different PRRs based on the CS bitstream, which is the second major step in HTR. Section 3.5 then describes how to perform CR of hardware tasks, which is the third major step in CSR and HTR. Next, Section 3.6 discusses the portability of our on-chip CSR and HTR across FPGA device families. Finally, conclusions from the first two phases of this research are summarized in Section 3.7.

#### 3.1 CSR and HTR Overview

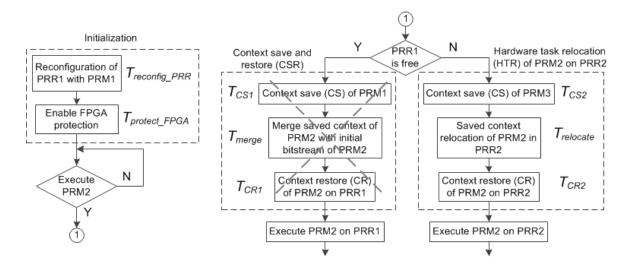

We explain CSR and HTR using a system with two heterogeneous PRRs. PRR1 is a candidate PRR for PRM1 and PRM2, and PRR2 is a candidate PRR for PRM2 and PRM3. Even though this is a small example, this system is sufficient for explaining CSR and HTR. Figure 3-1 depicts the CSR and HTR flows for this example. Even though not shown in Figure 3-1, we assume that PRM2 has already executed in PRR1, PRM2 was preempted and PRM2's context was saved, PRM3 is currently executing in PRR2, and PRR1 is ready to execute in PRM1.  $T_x$  denotes each step's execution time.

Initialization reconfigures PRR1 with PRM1 by transferring PRM1's initial partial bitstream for PRR1 from external storage to the device via the ICAP and enables FPGA protection to prevent re-initialization of flip-flops and BRAMs in the static region and PRRs on successive executions of the startup phase (Section 2.2.2). *T*<sub>reconfig\_prr</sub> and *T*<sub>protect\_fpga</sub> denote the execution times for these steps, respectively, and these times depend on the number of rows and columns in the PRR and FPGA, respectively.

PRM2 can either be resumed in PRR1 or relocated to PRR2. Since CSR requires less execution time than HTR, PRM2 will first attempt to resume execution in PRR1. For example, if PRR1 is free, or is executing a lower priority task and can thus be

preempted by PRM2 (i.e., PRM1 is lower priority than PRM2 in this case), CSR will resume PRM2 in PRR1 by: 1) CS of PRM1; 2) PRM2's saved context (CS bitstream) is merged with PRM2's initial partial bitstream to create the merged partial bitstream for PRR1; and 3) CR of PRM2 on PRR1. If PRR1 is not free or is executing a higher priority task (i.e., PRM1 is higher priority than PRM2 in this case), and PRR2 is available or executing a lower priority task (i.e., PRM3 is of lower priority in this case), HTR will relocate PRM2 to PRR2 by: 1) CS of PRM3; 2) relocate PRM2's saved context to PRR2; and 3) CR of PRM2 on PRR2.

In the following sections we elaborate the sequential major steps in CSR and HTR. The major steps in CSR are CS, merge of initial bitstream with CS bitstream, and CR, while the main steps in HTR are CS, saved context relocation, and CR.

## 3.2 Context Save (CS) of Hardware Tasks

CS is the first major step in both CSR and HTR. Before reading a PRM's flip-flops' values, the PRR's clock must be stopped to avoid potential setup/hold violations. Next, a sequence of commands (including GCAPTURE) is sent via the ICAP to initiate the capture process and subsequently unprotect the PRR.  $T_{pre\_cs}$  and  $T_{unprotect\_prr\_cs}$  denote the execution time for these steps, respectively, where  $T_{unprotect\_prr\_cs}$  depends on the number of rows and columns of the PRR. The PRR must be unprotected prior to capturing the flip-flops' and BRAMs' values since performing a capture over a protected PRR captures the flip-flops' and BRAMs' initial values and not the current values at the moment of stopping the PRR's clock. However, performing a capture over DSP columns will always give the DSPs' flip-flops' initial values because the DSP columns do not have specific configuration frames (of all 28) to read the current values of the DSPs' flip-flops' flip-flops' flip-flops' processed to the pro

flops, which is also confirmed in Jozwik's work [23]. We note that IOBs are not captured since the current version of the Xilinx tools no longer support IOBs in PRRs.

After the capture process is initiated and the PRR is unprotected, a sequence of commands executed in a program loop on the soft-core processor read and save the PRM's CLB LUTRAMs and CLB flip-flops' values into a temporary file on a frame-byframe basis. This software capture process's execution time depends on the number of frames containing PRM flip-flops, LUTRAMs, and BRAMs. Reading from Xilinx devices using the ICAP generates an extra dummy frame and one dummy word that must be read [50], but are later discarded. We read and save the PRM's BRAM values in a different temporary file, but not on a frame-by-frame basis since reading each BRAM column's contents (128 data frames) would greatly increase the CS execution time by reading an extra dummy frame and word for each valid frame. Instead, we read (23 + 1) data frames and one word for five iterations, and the sixth iteration we read (13 + 1)data frames and one word. The BRAMs' values must be captured in this way due to limitations imposed by the Linux driver for the HWICAP, which limits the data to a maximum of 4K bytes per readback [55].  $T_{cs\_prr}$  denotes the execution time to read the PRM's BRAMs, CLB LUTRAMs, and CLBs flip-flops' values, including the dummy frames and words and the time to save these values in the temporary files.

After completing the capture process, another sequence of commands (CMD RCAP) is sent to the device prior to re-protecting the PRR, which resets the internal CAPTURE signal to enable future CSs on the same or different PRR.  $T_{post\_cs}$  denotes the execution time for these commands. Then, the PRR is re-protected to prevent future execution of the startup sequence phase in another PRR from re-initializing the current

PRR's flip-flops' and BRAMs' values.  $T_{protect\_prr\_cs}$  denotes the execution time of this step. Next, a sequence of commands frees the ICAP for subsequent use by the current PRR or another PRR.  $T_{desynch}$  denotes the execution time for these commands.

Finally, another program loop executed on the soft-core processor discards the dummy frames and words from the temporary files and saves the PRM's context in a file (CS bitstream). The size of the CS bitstream in 32-bit words is denoted as 1+N+N\*41, where N is the number of frames read and that contain the PRM's flip-flops', LUTRAMs', and BRAMs' values. The first word in the CS bitstream specifies N's value, the following N words specify the N different frame address values that contain the flip-flops', LUTRAMs', and BRAMs' values, and the final N\*41 words are the contents of the N frames. T<sub>CS bitstream</sub> denotes the execution time to generate the CS bitstream.

Thus, the total execution time for CS (denoted as  $T_{cs}$ ) is:

$$T_{cs} = T_{pre\_cs} + T_{unprotect\_prr\_cs} + T_{cs\_prr} + T_{post\_cs} + T_{protect\_prr\_cs} +$$

$$T_{desynch} + T_{cs\_bitstream}$$

(3-1)

### 3.3 Merge of Initial Bitstream and Saved Context

The merge process is the second major step in CSR. The merge process in CSR updates a PRM flip-flop/LUTRAM/BRAM bit in the scheduled PRR with the PRM flip-flop/LUTRAM/BRAM bit from the CS bitstream. Figure 3-2 depicts these bitstream manipulations, which merge the CS and initial bitstreams at the 32-bit word level updating multiple flip-flop/LUTRAM/BRAM bits, and only on those words within a frame where context bits are involved. The example in Figure 3-2 has been reduced to eight bits for clarity.

To understand the bitstream manipulations in CSR, we use Table 3-1, that shows the truth table for CSR's merge process, expressed as  $f = (cap \land msk) \lor (ini \land /msk)$ ,

where cap is the captured value, ini is the flip-flop/LUTRAM/BRAM bit value in the initial partial bitstream, and msk denotes if the bit is part of the saved context where msk = 1 updates ini with cap and msk = 0 retains ini's value.

For the example in Figure 3-2, only the bit positions with msk = 1 will be updated with the value of cap in the same bit positions. Therefore, bits 7, 5, 3, and 1 will be updated producing a final f word (in binary) equal to 00111100.

The merge is executed as a program loop in the soft-core processor, where the loop's execution time is dictated by the number of words that contains the task's context in the CS bitstream. After the merge, the merged partial bitstream is saved to a file.  $T_{merge}$  denotes the execution time for the merge process, including the time to save the file.

### 3.4 Saved Context Relocation of Hardware Tasks (HTR)

The saved context relocation is the second major step in HTR. The bitstream manipulations required for relocating the saved context (i.e., HTR) is similar to the merge process in CSR [35]. HTR updates a PRM flip-flop bit in the scheduled PRR with the PRM flip-flop bit from the CS bitstream. Figure 3-3 and Figure 3-4 depict these bitstream manipulations, which merge the CS and initial bitstreams at the 32-bit word level based on two cases: update a single flip-flop or multiple flip-flops. Figure 3-3 shows the update of a single flip-flop value for HTR, and Figure 3-4 shows multiple updates of flip-flop values for HTR. All examples have been reduced to five bits for clarity.

HTR cannot use the expression *f* used in CSR (Section 3.3) for context relocation. HTR requires two *msk*'s, one for the saved context and the other for the initial partial bitstream in the scheduled PRR. In HTR, the context relocation for flip-flops

is expressed as  $g = (cap \land ms) \lor (inid \land /md)$ , where cap is the flip-flop's captured value, ms denotes if the flip-flop is part of the saved context, inid is the flip-flop's value in the initial partial bitstream for the scheduled PRR, and md denotes if the flip-flop in the merged bitstream needs to be updated. md = 1 updates inid with cap, provided that ms = 1, and md = 0 retains inid's value. In Figure 3-3 and Figure 3-4, bitms and bitmd denote the bit position of ms and md and the expression bitms - bitmd denotes the distance between these bits' positions in a 32-bit word. If  $bitms - bitmd \ge 0$ ,  $(cap \land ms)$  is right-shifted bitms - bitmd bit positions using  $shr(cap \land ms)$ , else,  $(cap \land ms)$  is left-shifted bitmd - bitms bit positions using  $shl(cap \land ms)$ . Updating multiple flip-flops in a word boundary in the merged bitstream (Figure 3-4) is done sequentially, and each update does not necessarily have the same cap and ms words as shown.

Context relocation for LUTRAMs and BRAMs follows the same procedure as the merge process in CSR (Section 3.3), but using the expression g, updating multiple bits in a word boundary and only on those words within a frame where context bits are involved without performing the shifting of  $(cap \land ms)$ . Since the LUTRAM and BRAM bits for the PRMs being relocated to different PRRs have the same bit positions within the words, there is no need to calculate the distance between the bit's positions or shift  $(cap \land ms)$  as is required for flip-flops. Also, the words' positions within a frame that include LUTRAM and BRAM bits are grouped consecutively, and the LUTRAMs and BRAMs' bits are saved in consecutive frames. This layout allows us to reduce the relocation time when LUTRAMs and BRAMs are included in a PRR, since alternatively performing context relocation for LUTRAMs and BRAMs using the expression g, but

updating bit-by-bit (as done with flip-flops) would incur prohibitively high context relocation execution times (on the order of seconds).

The context relocation is executed as a program loop in the soft-core processor, where the loop's execution time is dictated by the number of PRM flip-flops in the CS bitstream. After the relocation, the merged partial bitstream is saved to a file. *Trelocate* denotes the execution time for the context relocation (HTR), including the time to save the file.

### 3.5 Context Restore (CR) of Hardware Tasks

CR is the last major step in both CSR and HTR. Before CR, the scheduled PRR must be unprotected to allow initialization of the PRR's flip-flops with the new values in the merged partial bitstream, but the remainder of the FPGA must remain protected.  $T_{pre\_cr}$  denotes the execution time of the sequence of commands sent via the ICAP before unprotecting the scheduled PRR and  $T_{unprotect\_prr\_cr}$  denotes the execution time to unprotect the scheduled PRR. Next, the scheduled PRR is reconfigured via the ICAP by sending the merged partial bitstream, which has the same structure as the initial partial bitstream as shown in Figure 2-2, with the exception that no CRC is generated, and is replaced by the RCRC command.  $T_{update\_prr}$  denotes the execution time to transfer this new partial bitstream to the scheduled PRR.

Even though omitting the CRC introduces the possibility of reconfiguration errors, it is a valid solution for small partial bitstreams and when the FPGA is not exposed to a harsh environment, such as high radiation levels. Toggling GSR is more time efficient than generating the CRC on the fly in software, and generating the CRC with custom hardware incurs hardware overhead (1,218 flip-flops and 5 BRAMs for the Virtex-4 [24]), which may decrease the system's maximum operating frequency. Since there is no

CRC in the final words (Figure 2-2), the only way to initialize the PRR's flip-flops' and BRAMs' values with the PRM's saved context is to force the execution of the startup sequence phase by toggling the GSR signal (Section 2.2.2). *T*<sub>startup</sub> denotes the execution time of the startup sequence phase, which includes the time to toggle GSR and the elapsed time until the signal EOS is asserted. After the startup sequence phase, the scheduled PRR is reconfigured with the PRM's relocated context and is ready for execution.

Finally, it is necessary to protect the scheduled PRR to prevent future startup sequence phases to other PRRs from re-initializing the scheduled PRR's LUTRAMs, BRAMs, and flip-flops' values. *T*<sub>protect\_prr\_cr</sub> denotes the execution time for this step.

Thus, the total execution time for CR (denoted as  $T_{cr}$ ) is:

$$T_{cr} = T_{pre\_cr} + T_{unprotect\_prr\_cr} + T_{update\_prr} + T_{startup} + T_{protect\_prr\_cr}$$

(3-2)

# 3.6 CSR and HTR Portability across FPGA Device Families

No prior work addressed CSR/HTR portability across different FPGA device families, especially for 2-D different-sized heterogeneous PRRs, since prior works on on-chip BR/HTR and off-chip HTR have limitations or impose constraints that prevent implementation of HTR that can be easily ported to other FPGA device families with minimum changes.

Prior BR works [9][10][25][36][39][41][42] using on-chip custom hardware for 2-D homogeneous PRRs are complex and not portable because using custom hardware requires special constraints. These constraints require specific physical positions of inputs and outputs with respect to PRRs, no signals from static region must be routed through PRRs, and a communication bus between the custom hardware and all PRRs. Additionally, using custom hardware for on-chip BR works only for custom PRR sizes

and PRR resource organizations, and is not applicable to arbitrary PRR size/resource organization.

Prior off-chip HTR works [26][29] are not portable across FPGA device families, because off-chip HTR requires the FPGA to be attached to a host CPU with a dedicated host CPU-FPGA communication bus. Even though some FPGAs provide high speed communication bus signals to reduce the host CPU-FPGA communication overhead, this solution is expensive, requiring additional hardware (e.g., small form-factor pluggable (SFP) transceivers), and the high speed communication bus are not available in all FPGA device families. Also, using a dedicated host CPU-FPGA communication bus requires a special driver for the host CPU-FPGA communication, which in turn limits the implementation of HTR in an autonomous system on FPGAs. Additionally, using a bare-metal solution (no operating system on FPGA, and attached to a host CPU) limits HTR portability across different FPGA device families, because using a bare-metal solution would not be able to accomplish the bitstream manipulations (Section 3.3 and Section 3.4) efficiently, limiting the implementation of CSR and HTR.

Prior on-chip HTR works from Iturbe et al. [17][18][19] for 2-D heterogeneous PRRs also are not portable across FPGA device families. Iturbe's works used BRAMs (which are location-specific in the FPGA's fabric and limited in number) as buffers to hold input and output values for each hardware task, and PRRs must to be placed near to each other in the FPGA's fabric in order to copy the output values (from the output buffer) from one task to another task, using a custom hardware DRT block.

We note that a fixed on-chip custom hardware-based HTR between 2-D heterogeneous PRRs is extremely complex, because a large variety of PRR resource

distribution combinations in the PRR columns prevents the implementation of a fixed on-chip hardware-based HTR. A custom hardware implementation for establishing the mapping of flip-flops', LUTRAM bits', and BRAM bits' positions (for CR purposes, Section 3.4) between 2-D heterogeneous PRRs would be extremely difficult to implement (if not, impossible) with fixed hardware, resulting in excess area overhead and affecting the tasks' maximum operating frequencies. Also, the on-chip custom hardware for HTR may not be portable across same/different FPGA device families.

We note that our HTR approach for 2-D heterogeneous PRRs is a simpler, but not necessarily more efficient with respect to execution time, and more complete than prior works [17][18][19]. These works copy only the results computed by a hardware task (saved in an output buffer implemented with BRAMs), using a DRT block [19], to the input buffer (implemented with BRAMs) of the relocated task, while our approach relocates the entire task's context (i.e., the saved flip-flop, LUTRAM, and BRAM values required by the saved hardware task (Sections 3.2 to 3.5).

Our on-chip software-based CSR/HTR on 2-D heterogeneous PRRs is also portable across FPGA device families. We enable CSR/HTR portability by having a design specification that does not use special constraints (i.e., there is no special communication bus between the reconfiguration controller and the PRRs, there is no host CPU-FPGA communication bus, and there are no limitations with respect to PRR size/location/resource organization). Also, CSR/HTR portability is ensured by using a portable language for the CSR/HTR software application to be used with different FPGA device families. For our CSR/HTR application, we use the standard C language, and we

use configuration files selected for a device's specific architecture, where these configuration files are selected at compilation time.

The configuration files (\*.far) used in our CSR/HTR application specify the FAR addresses for each resource column (CLB, DSP, etc.) per row in the specific FPGA device. The bram.far, clb.far, clk.far, dsp.far, and iob.far used in our HTR software specify the FAR addresses for all of the BRAM, CLB, CLK, DSP, and IOB columns in the FPGA, respectively. For example, the Xilinx Virtex-5 LX110T (Figure 2-1) has eight rows and 5, 54, 1, 1, and 3 BRAM, CLB, CLK, DSP, and IOB columns per row, respectively, generating 40, 432, 8, 8, and 24 32-bit words for the bram.far, clb.far, clk.far, dsp.far, and iob.far files, respectively.

Also, we use a C header file (htr.h) to define all of the ICAP commands and the commands' codings using the #define directive for the Virtex-5 FPGA device family. The htr.h file also includes the sequence of ICAP commands used in CSR and HTR for FPGA/PRR protection and PRR unprotection, CS, and CR, where all of these sequences are organized as arrays, and the definition of the number of configuration frames per each resource type (CLB, DSP, etc.) for the Virtex-5 FPGA device family. For HTR compatibility across FPGA device families, changes to htr.h are needed to include the definition of the ICAP commands and the commands' codings, the sequence of ICAP commands for CSR/HTR, and the number of configuration frames for each type of resource for different FPGA device families. Then, at compilation time, these definitions will be selected for the FPGA device family where CSR/HTR will be executed.

Additionally, before CSR/HTR begins execution, pre-processing extracts the information for each PRM/PRR mapping using the \*.far files, the partial bitstreams, and the logic location file (\*.II) generated when the partial bitstreams are created. Each line in the plain text logic location file generated by the Xilinx tools contain the frame addresses, the LUTRAM bits', BRAM bits' and flip-flops' positions in the frames, and the LUTRAMs', BRAMs', and flip-flops' net names for the entire project, and the lines in the \*.II file were ordered by frame (Xilinx's default). Then, the pre-processing obtains the size and position of the PRRs, the column type (CLB, etc.) order inside PRRs, all FAR addresses involved in the PRRs, and the position of all of the flip-flop, LUTRAM, and BRAM bits inside the partial bitstreams for each PRM.

## 3.7 Summary

In this chapter, we have presented on-chip CSR and HTR software, which correspond to the first and second phase of this research, respectively. CSR enables hardware multitasking in the same 2-D heterogeneous PRR, and is able to preserve the context of preempted hardware tasks upon tasks resumption, without disrupting operations in the static region and other PRRs. HTR leverages CSR and enables the relocation of hardware tasks' contexts between different-sized 2-D heterogeneous PRRs in order to maximize PRRs utilization in the same FPGA and maximize tasks throughputs by providing more candidate PRRs for hardware tasks to resume operations.

Our on-chip software-based CSR/HTR for 2-D heterogeneous PRRs executes in an FPGA as an autonomous system (i.e., not using a host CPU-FPGA communication bus), using the MicroBlaze soft-core processor as a reconfiguration controller.

Our on-chip CSR/HTR is portable across FPGA device families with minimum changes (to file htr.h), by not using specific constraints in the design specification, not using a dedicated communication bus between the static region and PRRs or between PRRs, using a portable language (standard C), using the \*.far files for the selected FPGA device at compilation time, and using the \*.ll file and partial bitstreams generated by the Xilinx tools in order to obtain all PRMs/PRRs mapping information, such as the positions of PRRs in the FPGA fabric, size of all PRRs, column type order inside each PRR, and position of all PRMs' flip-flop, LUTRAM, and BRAM bits inside the partial bitstreams, which is all the information a system designer needs for CSR/HTR.

Next, Chapter 4 continues on by extending our CSR/HTR software in order to enable tasks' context relocation across multiple physically-distributed FPGAs which are networked-interconnected, providing additional improvements in resource usage per FPGA and task throughput due to more candidate PRRs per task.

Table 3-1. Truth table for the CSR merge process

| ini | cap | ) | msk | 1 | f |

|-----|-----|---|-----|---|---|

|     | )   | 0 | (   | 0 | 0 |

| (   | )   | 0 | •   | 1 | 0 |

| (   | )   | 1 | (   | C | 0 |

| (   | )   | 1 | •   | 1 | 1 |

| •   | 1   | 0 | (   | C | 1 |

| •   | 1   | 0 | •   | 1 | 0 |

| •   | 1   | 1 | (   | C | 1 |

| •   | 1   | 1 | •   | 1 | 1 |

Figure 3-1. On-chip context save and restore (CSR) and hardware task relocation (HTR) flows

```

bit 7 6 5 4 3 2 1 0

msk = 1 0 1 0 1 0 1 0 1 0

/msk = 0 1 0 1 0 1 0 1 0 1

cap = 0 0 1 0 1 0 1 0 0

ini = 0 0 1 1 0 1 0 1 0

cap \land msk = 0 0 1 0 1 0 0 0

ini \land (/msk) = 0 0 0 1 0 1 0 0

f = 0 0 1 1 1 1 0 0

```

Figure 3-2. Multiple flip-flop updates for CSR merge process

Figure 3-3. Single flip-flop update for context relocation (HTR) process

```

bit 4 3 2 1 0

bitms = 0

bit 4 3 2 1 0

bitms = 1

ms = 0 \ 0 \ 0 \ 1

bitmd = 2

ms = 0 \ 0 \ 0 \ 1 \ 0

bitmd = 3

cap1 = 0 1 0 1 1

bitms - bitmd = -2

cap2 = 1 1 0 0 1

bitms - bitmd = -2

inid = 0 1 0 0 1

→ inid = 0 1 1 0 1

md = 0 \ 1 \ 0 \ 0 \ sh7(cap2 \land ms) = 0 \ 0 \ 0 \ 0 \ 0

md = 0 \ 0 \ 1 \ 0 \ 0 \ sh7(cap1 \land ms) = 0 \ 0 \ 1 \ 0 \ 0

/md = 1 \ 1 \ 0 \ 1 \ 1

inid \wedge (/md) = 0 \cdot 1 \cdot 0 \cdot 0 \cdot 1

/md = 1 \ 0 \ 1 \ 1 \ 1

inid \wedge (/md) = 0 0 1 0 1

cap1 \land ms = 0 \ 0 \ 0 \ 1

g = 0 \ 1 \ 1 \ 0 \ 1 \rightarrow cap2 \land ms = 0 \ 0 \ 0 \ 0

g = 0 \ 0 \ 1 \ 0 \ 1

```